AMD Ryzen 9 5950X, 5900X & Ryzen 7 5800X recenzija

Datum objave 05.11.2020 - Krešimir Matanović

Zen 3 mikroarhitektura i Ryzeni 5000 serije

Malo manje od četiri godine nakon lansiranja prve generacije Ryzen procesora i potpuno nove Zen mikroarhitekture, AMD na tržište donosi procesore s evoluiranom Zen 3 arhitekturom koja puno toga obećava. Za početak, tvrde kako su konačno istjerali konkurenciju iz posljednje utvrde koju su držali – broju izvršenih instrukcija po ciklusu ili taktu. Jednojezgrene performanse su bile malo slabija točka Zena, no sada je i to riješeno, s kako AMD tvrdi 19-postotnim ubrzanjem. Danas testiramo čak tri od ukupno četiri predstavljena modela. Najjače Ryzene 5950X i 5900X s 32, odnosno 24 logičke jezgre, te Ryzena 7 5800X sa šesnaest. Zen 3 arhitektura na kojoj su bazirani donosi unificiranje CCX/CCD dizajna, koji sada sadrži osam jezgri i 32 MB L3 memorije unutar istog complexa.

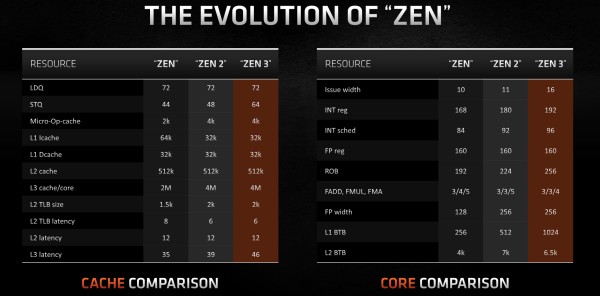

Četvrta je ovo generacija Zen arhitekture koja uključuje Zen, Zen+ i Zen 2 evolucije koje su AMD-u donijele novi život nakon Bulldozer arhitekture i njenih izvedenica. U četiri su godine na mainstream desktop tržište uspjeli donijeti procesore sa 16 jezgara što je do nedavno bilo nezamislivo. Sada sa Zenom 3 dodatno unificiraju početni dizajn, dovode lagane arhitekturalne izmjene i donose povećanje performansi gdje su bili malo “tanki” – IPC. Za svaki je procesor bitan podatak koliko instrukcija može izvršiti u jednom ciklusu (ili taktu). Ryzeni su u protekle tri generacije malo kaskali za Intelom u tom pogledu, no ova nova četvrta (premda serija nosi ime 5000), donosi 19% povećanja IPC-a u prosjeku u odnosu na Zen 2 (AMD-ovo interno mjerenje 25 mješovitih benchmarka na istom 4 GHz taktu), bazirano samo na arhitekturalnim promjenama. Uz to, novi procesori donose više radne taktove, nove 8-jezgrene komplekse (do sada 4-jezgreni), novu topologiju L3 memorije, a zadržavaju isti 7-nanometarski proces proizvodnje (TSMC).

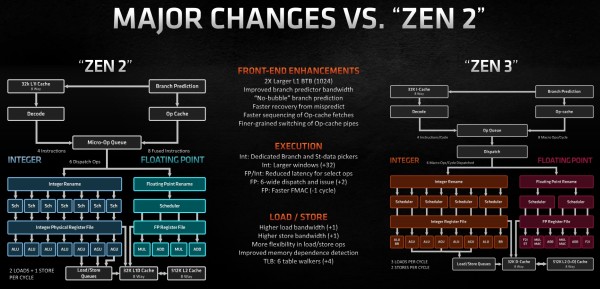

19% povećanja IPC-a u prosjeku je postignuto s tri arhitekturalne promjene. Prva je uključivala front-end poboljšanja na boljem predviđanju grananja, bržem “oporavku” nakon krivog predviđanja i poboljšanjima u radu s operacijskom priručnom memorijom. Druga je poboljšanje u izvođenju tj. radu s cijelim brojevima i brojevima s pomičnim zarezom. Treće, i ne manje bitno je poboljšanje u load/store operacijama kojima je povećana propusnost, fleksibilnost te memory dependance tehnika predviđanja gdje procesor “špekulira” koje će load/store operacije izvršiti out-of-order, a koje ostaviti za in-order izvršavanje.

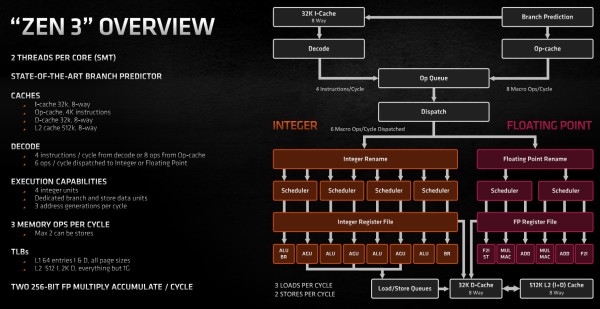

Front-end poboljšanja donose brže predviđanje grananja, brže prebacivanje između operacijske i instrukcijske priručne memorije, brži oporavak nakon krivog predviđanja grananja te različite tweakove na preciznosti grananja. Fetch/Decode operacije su ubrzane boljim predviđanjem grananja (Ryzeni korise TAGE predictor), redistribucijom BTB-a (branch target buffer), za nižu latenciju predviđanja (L1 BTB – 1024 unosa, L2 BTB 6.500 unosa), povećan je ITA na 1.500 (intirect target array), niža je latencija krivog predviđanja, i eliminirano je stvaranje “mjehura” na većini predviđanja. Optimizirana je L1 instrukcijska memorija (32KB), a poboljšan je prefetching i općenito upotreba memorije. Operacijska priručna memorija je poboljšana s bržim sekvenciranjem dohvata (fetch) i finijim granuliranjem prebacivanja između operacijske i instrukcijske priručne memorije.

Izvršna je jedinica poboljšana širim floating point i integer izdavanjem, bržim FMAC-om (fused multiply accumulate), širim “vremenskim prozorima” izvršavanja, i novim integer data pickerima. Izvršavanje operacija s cijelim brojevima (integer) je ubrzano povećanjem schedulera (96 vs. 92 unosa), zatim fizičkog registra (192 vs. 180 unosa), povećanjem izdavanja po ciklusu (10 vs. 7 (4 ALU-a, 4 AGU-a, jedna dedicirana grana i 2 St-data), a i ROB je povećan (256 vs. 224 unosa). Floating point izvršavanje je ubrzano novim 4-cycle FMAC-om, proširenom propusnošću otpreme, odvojenim F21/Store jedinicama i povećanim schedulerom.

I za kraj, Load/Store jedinice imaju povećani store queue (64 vs. 48 unosa), zatim L2 DTLB s 2.000 unosa, 8-way L1 podatkovnu priručnu memoriju kapaciteta 32KB (tri puta više operacija s memorijom po ciklusu, do tri load operacije po ciklusu i do dvije store operacije po ciklusu). Brže je kopiranje kratkih nizova, poboljšan je prefetching, a bolje je i predviđanje store-to-load ovisnosti.

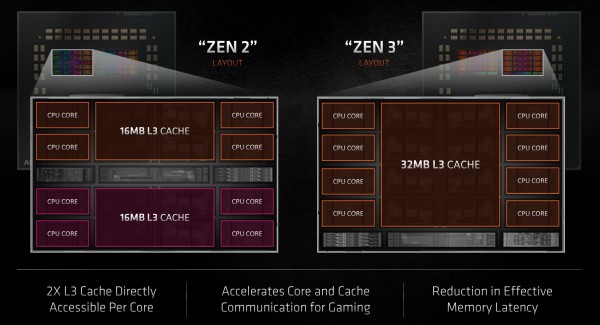

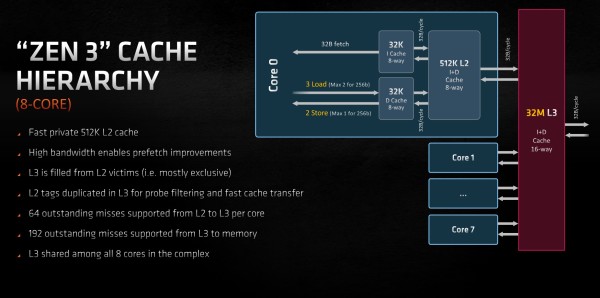

Velika novost je i u “pakiranju”. Prijašnja arhitektura CCX-a (core complex) je uključivala 4 jezgre i 16 MB L3 memorije, a sada jedan CCX ima 8 jezgara i 32 MB L3 memorije. Ovo je rezultiralo dvostrukim povećanjem L3 memorije kojoj svaka pojedina jezgra može pristupiti, ubrzavanjem komunikacije između jezgara i memorije, te znatno smanjenje efektivne latencije memorije – ranije je komunikacija između dva CCX-a išla preko IO jezgre, a sada kad je osam jezgri zajedno manje se koristi IO, što je brže, a i utrošak energije je manji.

Hijerarhija priručne memorije unutar jedne jezgre procesora je ostala ista, ali je poboljšanje vidljivo u Load/Store operacijama podatkovne memorije gdje je ostvaren skok s dvije na tri load operacije, i s jedne na dvije store operacije. I dalje je tu 512K L2 memorije, a i L1 – L2 – L3 komunikacija je ostala ista – 32 bajta po ciklusu. Naravno, sada jedna jezgra ima pristup duplo većoj L3 memoriji (16 vs. 32 MB) i to je veliki razlog povećanja IPC performansi kod single ili light-threaded aplikacija.

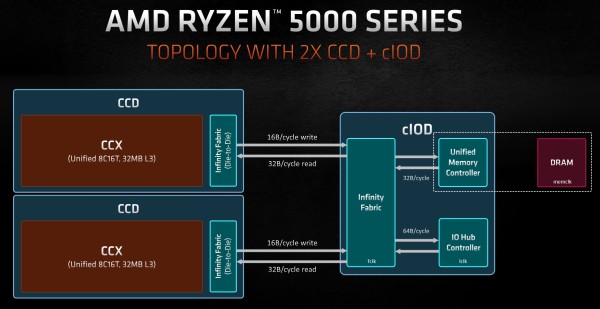

Novi Ryzeni 5000 serije i dalje imaju chiplet topologiju pakiranja, s po jednim ili dva CCX-a, odnosno CCD-a, te jednim cIOD-om. Velika razlika u odnosu na prošlu generaciju je što jedan CCD sada više ne sadržava dva CCX-a s po 4 jezgre nego samo jeda, a unutar njega je i infinity fabric, tj. komunikacijska međuspojnica koja je jednako fleksibilna kao i do sada. Ovime je eliminirana sva dosadašnja komunikacija između dva CCX-a, čime je smanjena core-to-core latencija i unutar CCX-a i između dva CCX-a kod 12 i 16-jezgrenih procesora. Jedan CCD je veličine oko 80.7 kvadratnih milimetara i sastoji se od 4,15 milijardi tranzistora.

cIOD, odnosni input/output jezgra je i dalje napravljena u 12-nanometarskom proizvodnom procesu, ima površinu od 125 kvadratnih milimetara i sadrži 2,09 milijardi tranzistora. Sadrži Infinity fabric, unificirani memorijski kontroler i I/O Hub kontroler. Toliko o arhitekturi i pakiranju, idemo na konkretne modele!

Forum

Objavljeno prije 1 minute

TES 4 OblivionObjavljeno prije 4 minute

LCDi, Plazme i ostali televizori - pročitaj prvi post prije postavljanja pitanjaObjavljeno prije 33 minute

Kućna struja, uzemljenje, osigurači, razvodiObjavljeno prije 1 sat

Procjena: PS4 nije slim sw 9.04Objavljeno prije 1 sat

Honor mobiteliNovosti

Instagam otključava značajku Edit Grid God (Uredi mrežu)

Instagram je društvena platforma bez koje mnogi mladi ljudi ne mogu svaki dan. Posebno je glavno bojno polje za online "ljepotice" i dijeljenje prekrasnih fotografija i stvaranje fantastične tipografije. Prije nekog vremena, IG je promijeni... Pročitaj više

Microsoft potvrdio: korištenje klasične verzije Outlooka može učiniti prijenosno računalo vrućim

Ako se vaše prijenosno računalo iznenada zagrije, ventilator se divlje vrti ili čak baterija brzo gubi napajanje, problem možda nije u računalu, već u krivnji Outlooka. Microsoft je nedavno potvrdio da greška u klasičnoj verziji Outlooka na... Pročitaj više

Intelov Arrow Lake-S Refresh procesor stiže početkom sljedeće godine

Nedavno, prema relevantnim otkrićima, Intelov procesor za stolna računala sljedeće generacije Arrow Lake-S Refresh trebao bi debitirati početkom 2026. Procesor će i dalje biti kompatibilan s postojećim LGA1851 socketima, što znači da korisn... Pročitaj više

Google pretraživanje: Brzina i pouzdanost nikad se nisu promijenili

Google potvrđuje da je njegova glavna misija osigurati da je tražilica uvijek spremna poslužiti korisnike, od traženja rezultata nogometne utakmice koja je u tijeku do ažuriranja udarnih informacija o oluji. U postu na blogu, Google je nagl... Pročitaj više

Intel nova Lake-S sljedeće generacije imat će LGA-1954 priključak

Nedavno je otkriveno da bi Intelov procesor sljedeće generacije, Nova Lake-S, mogao koristiti potpuno novi socket. Ako je to istina, to možda nije dobra vijest za sve koji su upravo kupili matičnu ploču Intel 800 serije s podrškom za LGA-18... Pročitaj više

Sve novosti