AMD Zen 2 arhitektura

Datum objave 26.06.2019 - Krešimir Matanović

Zen 2 arhitektura

Uvod

AMD udara iz svih oružja i paralelno s izlaskom novih grafičkih kartica i RDNA arhitekture, izlaze i novi Ryzen procesori treće generacije na Zen 2 arhitekturi. Zen 2 je nadogradnja na originalnu Zen arhitekturu, te donosi niz poboljšanja u mikroarhitekturi kroz koja ćemo proći u ovome članku. Procesori će sada imati više jezgri na mainstream platformu (16 vs. 8), napravljeni su u novom 7 nm proizvodnom procesu, a stiže i potpuno nova X570 platforma s PCIe 4.0 tehnologijom za nove Radeone.

Glavni ciljevi s novom su arhitekturom bili podizanje performansi, uvođenje novog proizvodnog procesa i omogućavanje skalabilnosti, tj. povećanje broja jezgara i I/O-a u postojećem Socketu AM4. Fokus je novog proizvoda su gameri, streameri i kreatori, a AMD tvrdi da su single thread performanse su rasle u svim segmentima u odnosu na Ryzen 7 2700X. Radili su i s Microsoftom na poboljšanju performansi u komunikaciji operativnog sustava i procesora, pa May 2019 update Windowsa 10 donosi Topology Awareness u scheduleru, koji će sada puni threadove u jednom CCX-u prije prijelaza na novi CCX ili CCD. Radili su na poboljšanju bržeg podizanja taktova (Faster clocks ramps (CPPC2)) pa je postignuto ubrzanje od gotovo 20 puta, tj. selekcija takta je skraćena s dosadašnjih 30 ms na jednu do dvije milisekunde. To znači kako su se inicijalne performanse (burst) povećale za oko 6 %, što će biti primjetno prilikom lansiranja aplikacija.

Radilo se i na priručnoj memoriji, pa je L3 poduplan, uz efektivnu latenciju memorije od 33 ns. To je rezultiralo s 21 % povećanja performansi u igrama - istovremeno je više podataka "bliže" procesoru, pa su i tu rasle performanse zbog ovisnosti igara o priručnoj memoriji. L3 memorija će se u novim procesorima stoga zvati Game Cache. Osim povećanja performansi igara, povećane su performanse i za kreatore, ubrzano je renderiranje, transkodiranje video materijala i slično.

Sve nove procesore će pratiti nikad više matičnih ploča na tržištu. Ako se sjetimo prve generacije Ryzena, proizvođači su bili malo sramežljivi, no sada su se dobro pripremili. Najavljeno je oko 150 različitih modela matičnih ploča s X570 čipsetom, a sada je i više premium modela nego ikad. Nove će X570 ploče biti unazad kompatibilne sa svim generacijama Ryzena, no bit će i skuplje no ikada. Naglašeno je da X570 nije nasljednik X470, već samo njegova modernija nadogradnja i kako će se X470 i dalje ravnopravno nuditi.

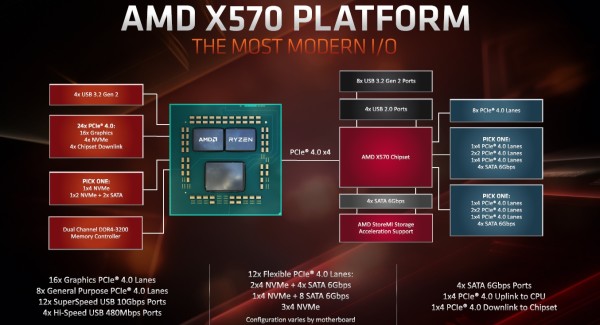

A kada je riječ o X570, to je svakako AMD-ov najmoderniji I/O procesor do sada, ali i općenito na desktop tržištu. Donosi 24 PCIe 4.0 stazice, četiri za NVMe, te ima podršku za DDR4 3200 memoriju. Naglašeno je da PCIe četvrte generacije neće donijeti velike razlike za igre, no kod "content creationa" će se osjetiti dodatna propusnost, a PCIe 4.0 je unazad kompatibilan i sa starijim generacijama.

Novost je da je BIOS overclocking poboljšan - pridodana je dodatna pažnja za olakšavanje overclockinga i razumijevanja pojedinih opcija s dodavanjem opširnih help tekstova, a to će biti zajedničko za sve X570 ploče.

Jedan od primarnih ciljeva kod nove platforme je bilo i poboljšanje overclockinga radne memorije. Omogućen je bolji integritet signala između procesora i memorije, a prvi podaci govore kako najbolji DDR4 moduli na zraku idu sve do 5.100 MHz pri latencijama CL18-21-21-56-1T. Za one koji više vole Windows softver, dolazi i novi Ryzen Master za treću generaciju procesora, koji između ostalog omogućava puni pogled na power stanja procesora, bolju kontrolu radne memorije itd.

Arhitektura

O Zen 2 arhitekturi smo slušali od Mikea Clarkea, AMD-ovog corporate fellowa i Zen arhitekta. Zanimljivost je da ona nije inicijalno bila namijenjena desktop procesorima, nego onima za servere. Razlog tome je što su inicijalna predviđanja bila kako neće moći ostvariti visoke taktove, no to se promijenilo i krajem je 2015. godine donesena odluka kako će u ovom obliku doći kao zamjena za originalnu Zen arhitekturu koja je osmišljavana od 2012. godine.

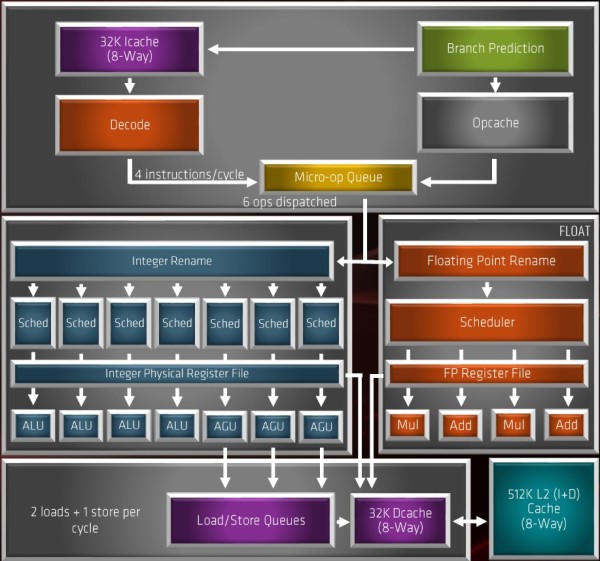

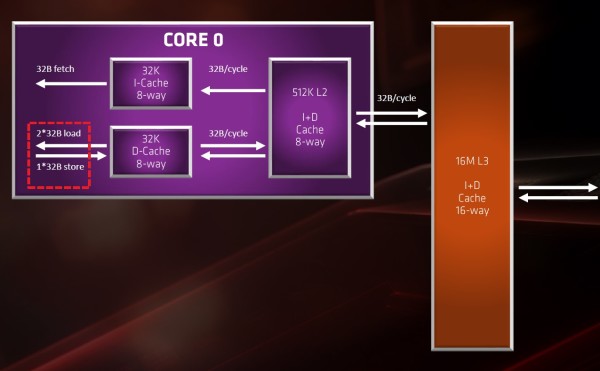

Zen 2 zadržava SMT dizajn, odnosno mogućnost obrade dva threada (dretve) po jezgri, dodano mu je TAGE predviđanje grananja, povećana Micro-Op priručna memorija (4K instrukcije), za duplo povećana L3 priručna memorija, ima četiri integer jedinice (jedinice za obradu cijelih brojeva, 180 registara, tri adresna generatora), odrađuje tri AGEN operacije po taktu (2x load/ 1x store), te ima dvije FPU jedinice (četiri cjevovoda - 2 add i 2 multiply operacije, podržava single-op AVX256). L1 priručne memorije je 32 KB instrukcijske i podatkovne po jezgri (8 way), te 512 KB L2 također 8 way.

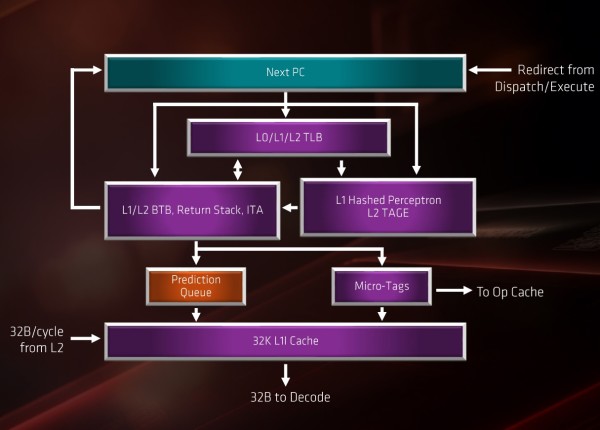

Kod dohvata instrukcija je poboljšano predviđanje grananja, dodan je novi TAGE "predictor", povećani su BTB-i (branch target bufferi) - za L0 je 16 unosa, za L1 512 (povećan s 256) i L2 je 7.000 unosa (povećanje s 4.000). ITA ili indirect target array podržava 1.000 unosa, a ukupno je smanjen nivo pogrešnih predviđanja za 30% u odnosu na prošlu generaciju, što smanjuje potrošnju. Posebna je pažnja pridodana L1 instrukcijskoj memoriji koja ima višu asocijativnost, poboljšan preddohvat i općenito je poboljšano iskorištenje memorije.

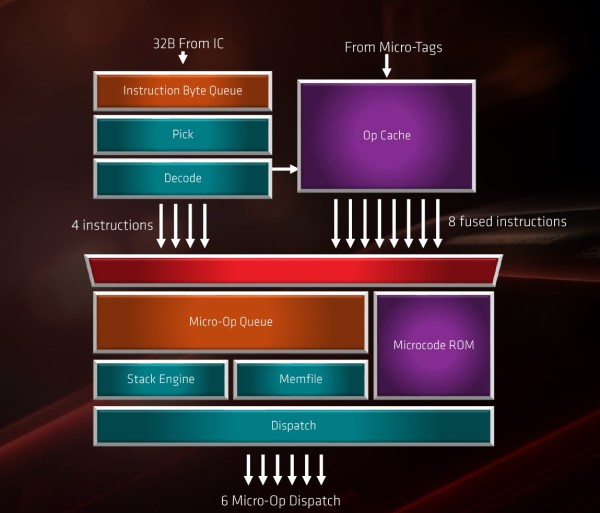

Na strani dekodiranja se nije ništa značajnije mijenjalo, i dalje je dispatch šest mikro operacija, no određenih napredaka ima pa one sada ulaze brže. Poboljšana je operacijska priručna memorija za instrukcije s micro Tagovima, povećan je kapacitet - do 4K za spojene instrukcije, poboljšano je samo spajanje instrukcija pa je na kraju povećana i sama efektivna propusnost.

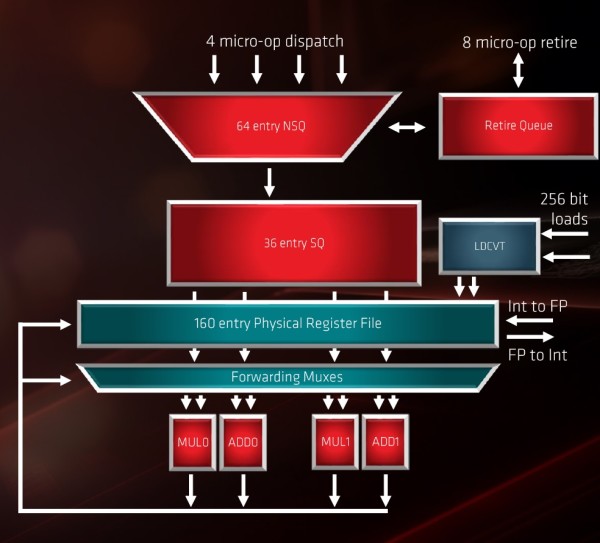

FP jedinica (Floating Point Unit) je arhitekturalno ostala ista, ali je dodana podrška za AVX2. Širina je izvršne jedinice povećana sa 128 bita na 256 bita, što je omogućilo single-cycle AVX2 kalkulacije. Kao i do sada, četiri mikrooperacije po ciklusu ulaze u fizički registar i dalje u četiri izvršne jedinice. Multiplikacijska je latencija pak smanjena s četiri ciklusa na tri, što je značajan napredak.

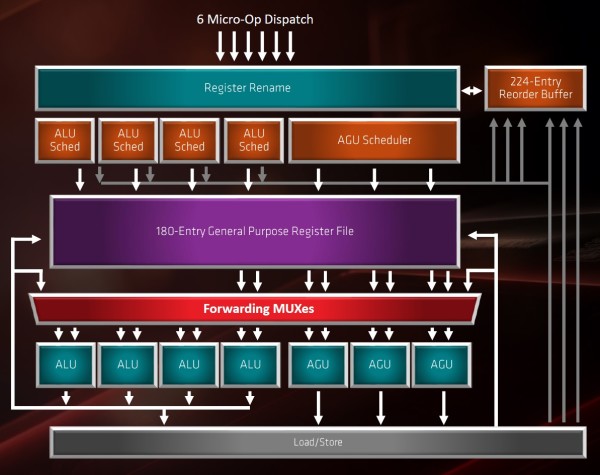

Na strani je izvršne jedinice cijelih brojeva došlo do promjena - scheduler je povećan sa 84 unosa na 92 (četiri ALU-a (aritmetičko logičke jednice sa 16 unosa) i jedan AGU(generator adresa)), Fizički je registar povećan sa 168 na 180 unosa, sedam je izvršnih portova (povećanje sa 6 - 4x ALU i 4x AGU), a ROB ili reorder buffer je povećan sa 192 na 224 unosa. Poboljšan je i SMT fairness kod ALU i AGU schedulera.

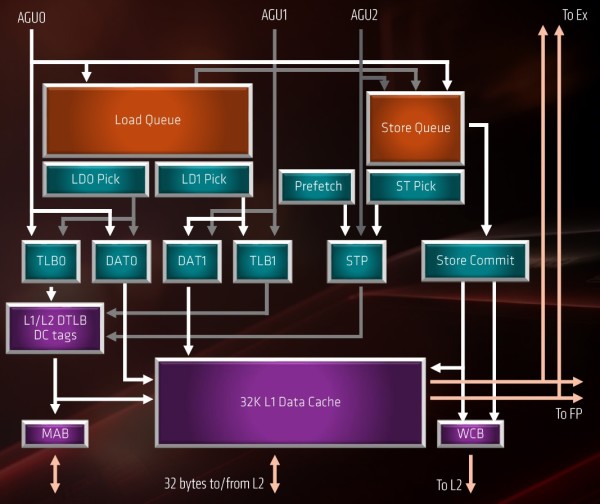

Load/Store jedinica je također doživjela promjene pa podržava dva 256-bitna čitanja i jedan 256-bitni zapis iz tri AGU-a, pri čemu AGU2 odrađuje samo zapis u memoriju, dok prva dva i zapis i čitanje. Kapacitet reda za zapis je povećan s 44 na 48 unosa, a povećani su i TLB-i za podatkovnu memoriju (translation lookaside buffer). Ukratko, Load/Store propusnost je povećana sa 16 bajta po ciklusu (taktu), na 32 bajta.

Kao što smo već mogli vidjeti, najveća promjena u sustavu priručne memorije je smanjenje L1 instrukcijske memorije sa 64 KB po jezgri na 32 KB, ali i povećanje asocijativnosti sa 4-way na 8-way, što je omogućilo povećanje broja unosa micro-op memoriju sa 2K na 4K. To bi u konačnici trebalo dati bolji balans performansi u sadašnjim i budućim radnim opterećenjima. L3 (non-inclusive priručna memorija) je povećana za duplo, s 8 MB po CCX-u na 16 MB, pri čemu je malo narasla latencija s 35 na 40 ciklusa. L3 je memorija prigodno nazvana Game Cache jer povećava performanse u igrama i to je jedno od "tajnih" oružja u sustizanju performansi Intelovih procesora. No, L3 nije povećan i samo radi igara, nego i radi novog Infinity Fabrica kako se komunikacija ne bi usporila. Dodane su nove tri instrukcije u priručnu memoriju, jedna od kojih je i QoS koji može particionirati L3 memoriju za različiti softver što Intel primjerice već koristi.

Pakiranje

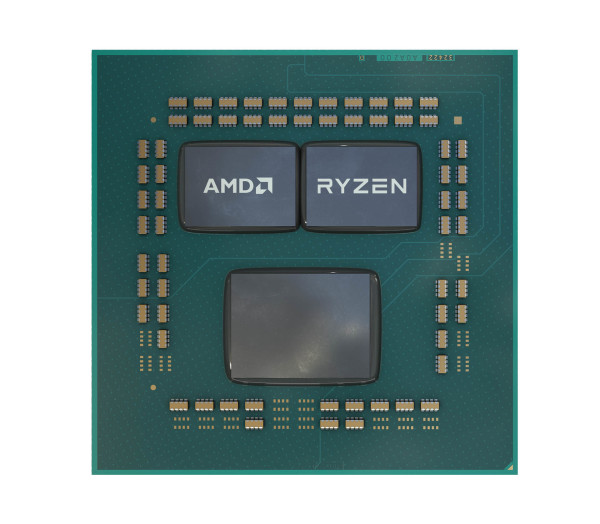

AMD je sa Zen 2 arhitekturom i Ryzen procesorima treće generacije prešao s monolitnog dizajna jezgre, na tzv. chiplet dizajn više jezgara na istom pakiranju.

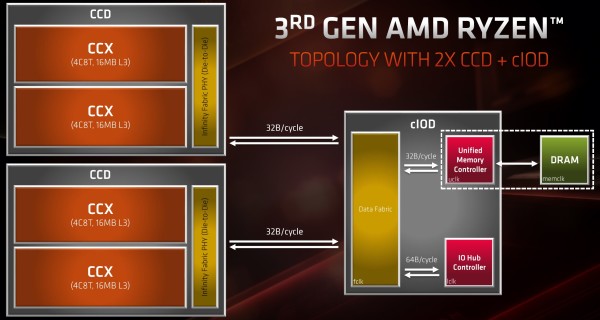

Korištena je dakle potpuno nova topologija, tj. pakiranje procesora s 1x CCD + cIOD ili 2x CCD + cIOD kombinacijom jezgri (die), te nova generacija tzv. Infinity Fabrica koji ih sve povezuje. Novi je IF dobio podršku za PCIe 4.0, a propusnost mu je povećana s 256 na 512 bita. Ukupna efikasnost je povećana za 27%, čime je smanjena i potrošnja. IF je sada na odvojenom taktu od DRAM-a, tj. uveden je 2:1 omjer pri čemu se IF usporava na pola brzine, pa će i overclockabilnost radne memorije biti bolja - trade-off je korištenje više logike.

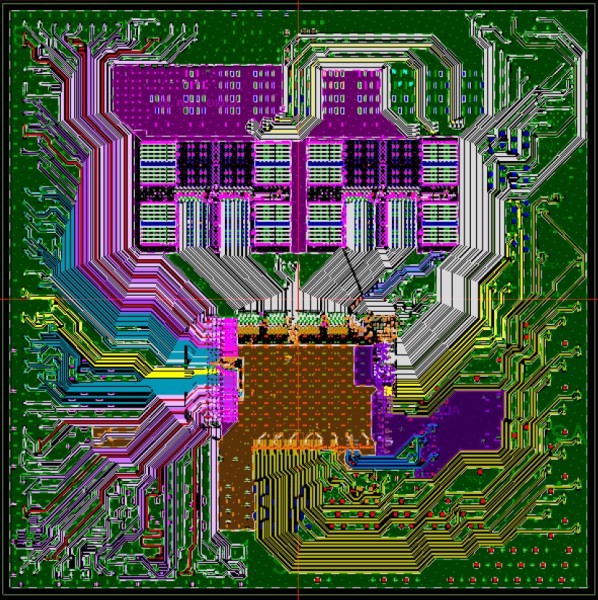

CCX dizajn u kojem se nalaze 4 fizičke jezgre je zadržan, a po dva su CCX-a (core complex) smještena u jedan CCD, no zbog novog je proizvodnog procesa jedan CCX sada 47% manji u odnosu 12 nm proces.. Novost je cIOD, tj. izmještanje I/O huba i unificiranog memorijskog kontrolera na zaseban dio (zasebna jezgra). I dok su CCX-i napravljeni od strane TSMC-a u 7 nanometara, bitno za znati je da je cIOD još uvijek u 12 nm procesu a proizvodi ga Global Foundries.

Tako će po novom chiplet dizajnu, ili Multi Die Packagingu, osam i manje jezgreni procesori imati jedan CCD i cIOD, a dvanaest i šesnaest jezgreni modeli dva CCD-a i cIOD.

Razlog korištenja ovakvog pakiranja procesora je što je na istom čipu teško kombinirati analogno sklopovlje, digitalno, kontrolere i ostalo pa će chiplet dizajn za sve biti budućnost i zamjena za Mooreov zakon.

U izradi ovakvoga procesora floor plan je bio ključan kako bi se zadržala AM4 kompatibilnost, a s druge strane PCIe 4.0 podrška je zahtijevala znatno više slojeva i vodova. To je zahtijevalo povećanje substrata s 8 i 10, na 12 slojeva.

Spojevi, tj. bump pitchevi su sada razmaku od 130 mikrometara u odnosu na 150 mikrometara kod 12 nm, a spojeva je na tisuće koji su se i dalje morali spajati na isti raspored pinova kao kod starije generacije.

Kod 7 nm se desilo još nešto zanimljivo, lemljeni su spojevi zamijenjeni bakrom na CCX-u, dok se lem i dalje koristi za cIOD. Bakreni kontakti su kompaktniji, bolje provode struju i omogućavaju istu visinu jezgri nakon spajanja. Za one koje to jako zanima TIM (thermal interface materijal), ili materijal koji veže jezgre i integrirani hladnjak (IHS) je zalemljeni Indium.

Novi dizajn je donio i neke nove probleme. AMD se samo kod pakiranja našao u zanimljivim logističkim problemima - jer kako prepoznati koja je jezgra za 1xCCD, a koja za 2xCCD dizajn, koji je procesor s jednim a koji s dva CCD-a nakon postavljanja IHS-a, kako prepoznati koji je poklopac za koji dizajn? Oprema u tvornicama u Maleziji i Kini nije jednostavno bila dizajnirana za chiplet dizajn, pa su i to morali mijenjati i prilagođavati se novom načinu izrade procesora.

AMD je će dakle ovo ljeto učiniti iznimno zanimljivo hardverašima s novom generacijom Ryzena, ali i Radeona i već 7.7. ćemo vidjeti što su nam to pripremili i kako sve radi u praksi.