Arhitektura jezgre – AMD Bulldozer

Datum objave 05.10.2011 - Krešimir Matanović

Bulldozer arhitektura - 1.dio

Bulldozer mikroarhitektura je primarno serverska, i dizajnirana je kako bi povećala skalabilnost u zahtjevnim "enterprise" primjenama. Na tržište će tako doći tri vrste procesora - dvije serverske - Valencia i Interlagos, te iz njih izvedeni Zambezi desktop modeli. Novi serverski, šesnaest jezgreni Bulldozeri, trebali bi osigurati 50% veću propusnost od postojećih 12 jezgrenih Opterona, a zadržati isti nivo potrošnje i termalne okvire. Poboljšana će biti virtualizacija, izvršavanje aplikacija baza podataka (više threadova), HPC korisnici će moći uštedjeti na prostoru zbog veće gustoće jezgri na manjem prostoru, a Cloud servisi će profitirati od velike memorijske skalabilnosti i naravno povećanja broja jezgri. Uz potpuno novu mikroarhitekturu, novost je i prelazak sa 45nm na 32nm Silicon-On-Insulator (SOI) Hi-K Metal Gate proizvodni proces (11 metalnih slojeva), AMD-ovog partnera Globalfoundriesa. Novi proizvodni proces tako omogućuje smještaj 33% više jezgri na istu površinu. To konkretno znači da će najjači desktop 8-jezgreni Bulldozer procesor imati nešto manju površinu od aktualnog 6-jezgrenog Thubana. Da, 16 je jezgri za sada rezervirano samo za serverske procesore, dok će desktop modeli imati 8, 6 i 4 jezgri ili 4, 3 i 2 Bulldozer modula kako će te kasnije saznati iz teksta.

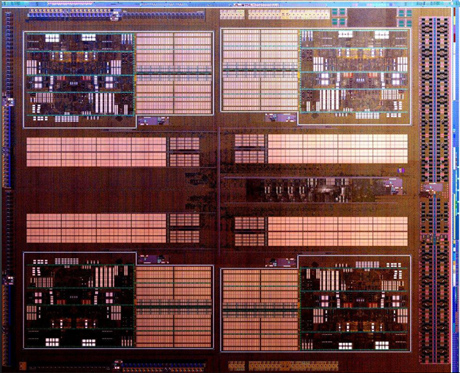

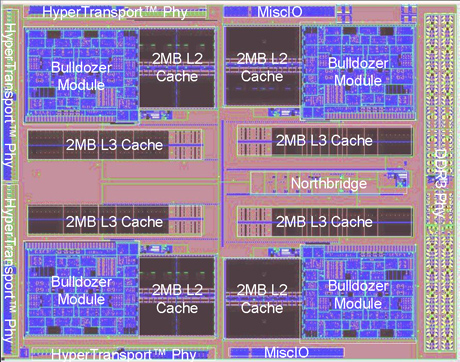

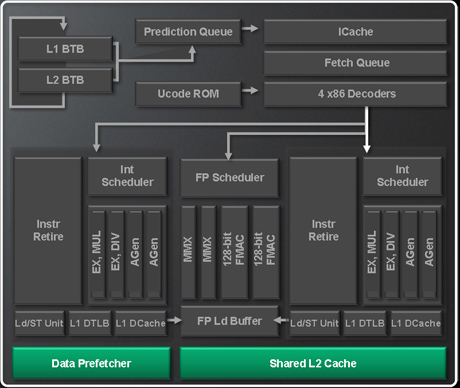

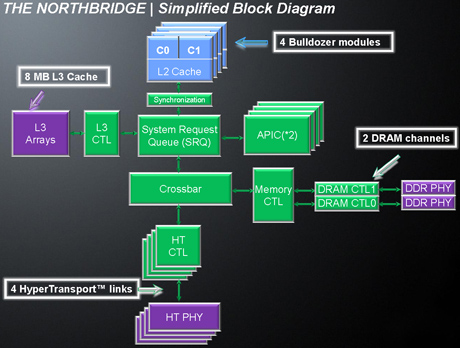

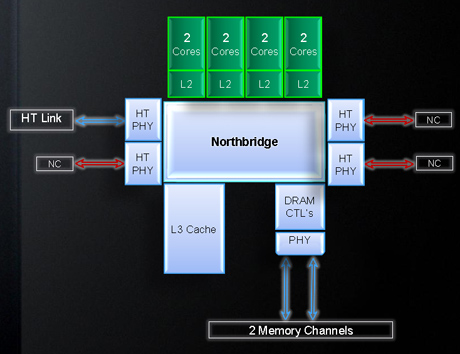

Novi dizajn mikroarhitekture, gdje postoje dvije integer jezgre u jednom modulu, koje dijele zajednički front-end (fetch i decode jedinice), zajedno s velikom L2 cache memorijom i FPU-om, AMD-u je omogućio modularni pristup "gradnji" proceosora. Ta mogućnost ostavlja felksibilnost gradnje i omogućuje procesore kao što su nadolazeći Opteroni 6200 (Interlagos) sa 16 jezgri, kao i 8-jezgrene Opterone 4200 serije (Valencia). Takav je princip naravno baza i za nadolazeće desktop procesore (Zambezi). Zambezi će dolaziti u konfiguraciji s maksimalno osam jezgri, tj. četiri Bulldozer modula sa po dvije integer jezgre u svakom modulu. Nove jezgre nose 15h naziv, u odnosu na prethodnu K10 arhitekturu koja je nosila naziv 10h. Takav 8-jegreni procesor na 315mm2 površine, sadržava četiri Bulldozer modula, veliki dio površine zauzima priručna memorija, a tu je i integrirani northbridge, DDR3 memorijski kontroler, četiri HyperTransport fizička sloja i različita I/O sučelja. Procesor ima ukupno 128 KB L1 podatkovne priručne memorije, tj. 16 KB po jezgri (64-byte cacheline, write-through, 4-way associative). Uz podatkovnu priručnu memoriju tu je i instrukcijska L1, a nje ukupno ima 256 KB (64 KB po modulu, 64-byte cacheline, 2-way associative). Drugostupanjska priručna memorija (L2) broji ukupno 8MB, tj. 2MB po Bulldozer modulu (1MB po jezgri, 64-byte cacheline, 16-way associative). I za kraj nam ostaje ukupno 8MB L3 priručne memorije, tj. 2MB po modulu (64-byte cacheline, 16-way associative, MOESI), koja je kontrolirana od strane integriranog Northbridgea. Integrirani northbridge (sjeverni most) kontrolira i dva kanala DDR3 memorije širine 72 bita, te četiri HyperTransport linka (16-bit receive/16-bit transmit).

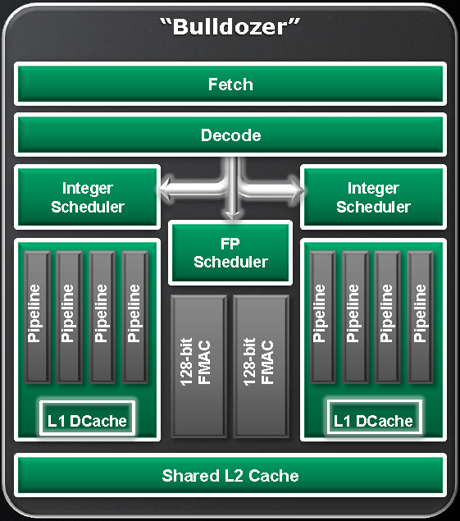

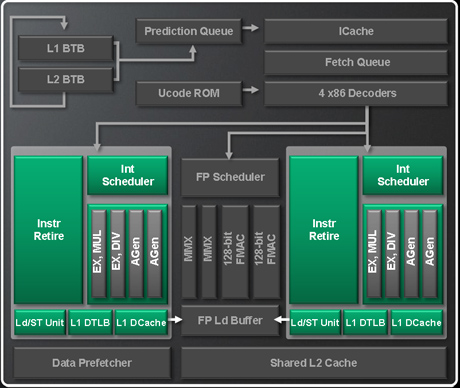

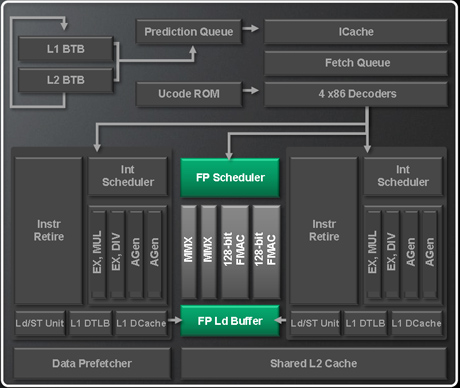

Arhitektura Bulldozer modula je zapravo ono što je najzanimljivije kod novih procesora. U jednom su modulu sadržane dvije izvršne jezgre, tj. jedan je modul u stanju odraditi dva threada simultano, a ostatak je logike dijeljen. No, ipak nije sve tako jednostavno. Svaka funkcija koja ne može na jednostavan način biti podjeljena (Integer pipelines, Level1 data caches) će postojati za svaku jezgru. Sve će se pak ostale funkcije (Floating point pipelines, Level2 cache) dijeliti između jezgara. Ovo omogućava da svaka od dvije jezgre koristi na svoj način funkcije viših performansi (floating point unit), jer se na taj način smanjuje ukupna aktivna površina jezgre.

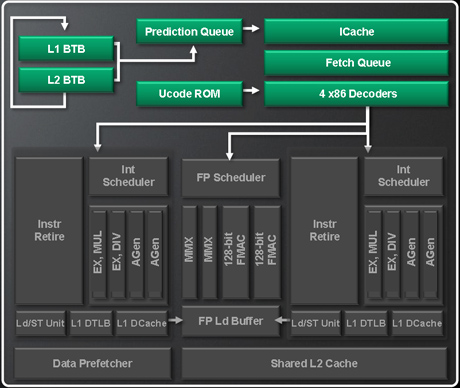

Novost u ovakvoj konstrukciji je i dijeljeni front-end (fetch i decode). Sastoji se od odvojenih cjevovoda za predviđanje i dohvat, instrukcijskog prefetcha određenog predviđanjem, 2-way instrukcijske priručne memorije veličine 64KB, 32-bajtne fetch jedinice, instrukcijskih TLB-a (translation lookaside buffer) u dva nivoa - prvi se sastoji od 72 unosa različitih veličina stranica, a drugi je s 512 unosa (4-way, 4K pages), i na kraju Branch fusiona.

Dvije jezgre su zapravo dvije odvojene integer jedinice od kojih se svaka sastoji od dvije ALU jedinice i dvije AGU jedinice, koje su sposobne odraditi četiri nezavisne aritmetičke i memorijske operacije po taktu. Prijašnji AMD-ov dizajn mogao je odraditi jedan therad po jezgri no imao je samo 3 cjevovoda, koji su dijelili ALU i AGU funkcije. Novim se dizajnom znatno povećavaju multithreaded performanse, uz povećanje jedne jezgre od oko 12%. Integer jedinice koriste "thread retire" logkiu, svaka jezgra ima svoj scheduler i koristi se Physical Register File preimenovanje registara (pomaže u održavanju malog broja fizičkih registara). Svaka jezgra ima 16K L1 priručne memorije, a podatkovni TLB podržava 32 unosa (cully associative). Load/store operacije se u potpunosti izvode out-of-order, sa dva 128-bit "punjenja" po ciklusu, jednim 128-bitnim spremanjem po ciklusu i redom od 40 unosa punjenja i 24 unosa spremanja.

FPU jedinica je dijeljena od strane dvije integre jezgre i radi na principu co-procesora s izvještavanjem matične jezgre o završetku operacije. FPU ima dvostruke 128-bitne FMAC (Floating Point Multiply/Accumulate) cjevovode i dvostruke 128-bitne Packed Integer cjevovode. FMAC jedinice rade s FMA (Fused Multiply Accumulate) instrukcijama, kao i sa standardnim FMUL (multiply) i FADD (add). Ipak, FMA operacija je snažnija jer dozvoljava kalkulacije tipa A = B x C + D. U standardnoj FP jedinici, ovo bi oduzelo dva ciklusa, jedan za množenje i jedan za zbrajanje. FMAC može odraditi i FMUL i FADD, dok tradicionalni dizajn imaju dedicirane putanje za te operacije. Kada se moraju izvršavati višestruke FADD ili FMUL operacije, optimizacja posla se sada vrši dijeljenjem posla na oba FMAC-am umjesto da na izvršenje čekaju jedna iza druge u redu. S Bulldozer arhitekturom, AMD koristi i moćnije FMA4 operacije koje se koriste u HPC (High performance computing) primjeni, a imaju četiri operanda. Uz standardne instrukcijske setove novost je podrška za SSSE3, SSE4.1, SSE4.2, AES-NI i AVX setove, a karakteristično samo za Bulldozer tu su i već spomenute FMA4 (HPC), te nove XOP instrukcije (numeričke, multimedijalne aplikacije i algoritmi koji se koriste za audio/radio).

Bulldozer arhitektura - 2.dio

16-way unificirana L2 priručna je memorija dijeljena od strane modula/jezgri. U 8 jezgrenom procesoru je ukupno ima 8MB, dok će ih u manje jezgrenim procesorima biti manje. TLB i page walker (8-way) podržavaju 1024 unosa, te odrađuju i instrukcijske i podatkovne zahtjeve. Višestruki su podatkovni prefetcheri, a L2 memorija je sposobna odraditi 23 izvanredna promašaja čitanja ili zapisa podataka za smanjenje latencije sistemske memorije.

Northbridge je kao što smo rekli integriran on-die, a sastoji se od System Request Queuea, Crossbara i memorijskog kontrolera. SRQ i Crossbar formiraju prometno središte dizajna, i rade kao usmjerivači zahtjeva iz bilo kojeg izvora prema određenoj destinaciji. Svaki memorijski kontroler provodi koherentnost priručne memorije i brine o pravilnom redoslijedu operacija za memorijski prostor koji posjeduje, raspoređujući tu odgovornost preko više jezgrenih ili više procesorskih sustava. Ovo tim sustavima omogućuje pravilno skaliranje, a ne gušenje na jednoj coherency/ordering točci u sistemu. Uz to naravno, kontroler šalje i read/write zahtjeve DRAM kontrolerima. DRAM kontrolera su dva po jezgri, podržavaju Unbuffered (UDIMM), Registered (RDIMM) i/ili Load-Reduced (LRDIMM) DDR3 memoriju, napona 1.50V, 1.35V i 1.25V (u ovisnosti o procesoru) maksimalne frekvencije rada do 1866MHz. Dodane su naravno i nove tehnike uštede električne energije (Low-voltage DDR3, fast self-refresh entry with internal clocks gated, aggressive precharge power down, tristate addr/cmd/bank w/chip-select deassertion, throttle activity for thermal or power reduction, put RX circuits in standby when no reads active, itd). Northbridge je zadužen i za L3 priručnu memoriju koje u dizajnu može maksimalno biti 8MB, koja se može particionirati, ECC je zaštićena (single-bit correct, double-bit detect), i ima funkciju Probe Filter (northbridge filtrira promet kako bi se poboljšala propusnost sistema). Četiri su HyperThransport linka, s brzom jednosmjernom signalizacijom (16-bits receive/16-bits transmit). Jedan 16-bitni link može biti podijeljen na dva 8-bitna linka, a maksimalna propusnost iznosi 6.4 Gigatransfera po sekundi po bitu. Broj linkova ovisi o čipsetu, pa tako AM3+ ima jedan link prema čipsetu, a serverski C32 i G34 imaju po tri, odnosno četiri linka.

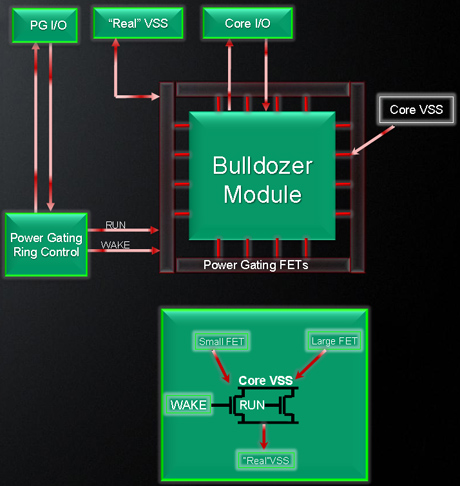

Bulldozer arhitektura je dizajnirana tako da ima efikasnu potrošnju, što je između ostalog postignuto i minimiziranjem površine jezgre dijeljenjem funkcionalnosti između dvaju jezgri. Uz to, svi su blokovi i strujni krugovi optimizirani za manju potrošnju korištenjem clock-gatinga i dinamičkog power-gatinga. Korišteni su i brojne značajke u firmwareu za uštedu energije - Core C6 State (CC6), Core P-states/AMD Turbo CORE, Application Power Management (APM), DRAM power management i Message Triggered C1E.

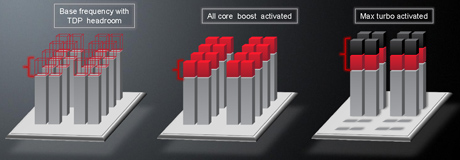

Sa strane baratanja potrošnjom energije još su dvije značajke vrlo važne - P-states i Turbo CORE. P-stanja definiraju višestruke točke frekvencije i napona za povećanje performansi, dok Turbo CORE djeluje na način da kada procesor radi ispod TDP-a, podiže napon i frekvenciju svih ili određenih jezgara na veći nivo, ali se naravno zadržava unutar TDP-a. Turbo CORE sada ima dva stanja - All Core Boost i Max Turbo Boost. I dok je All Core Boost preuzet sa starijeg dizajna, novost je Max Turbo Boost. On djeluje u slučaju manje nitnih aplikacija, tako da podiže frekvenciju određenih jezgri iznad All Core Boost vrijednosti. Kako to radi u praksi saznati će te kada nam bude dopušteno objaviti frekvencije procesora, a za sada toliko o ovoj tehnologiji.

Dijagram iznad prikazuje desktop varijantu Bulldozera kodnog imena Zambezi. Zambezi je kao što znamo namijenjen AM3+ platformi (990FX, 990X, 970 i SB950 čipseti), podržava low-voltage DDR3 memoriju, povećanu ILDT struju za više HyperTransport frekvencije (2 Ampera po Gen3 linku), te povećan IDDR napon (maksimalno 4 Ampera). Radna je memorija kao i do sada dvokanalna, a brzina je podignuta na 1866MHz. Kao što smo već rekli za desktop je procesore određen jedan komunikacijski HT link brzine 5.2 GT/s.

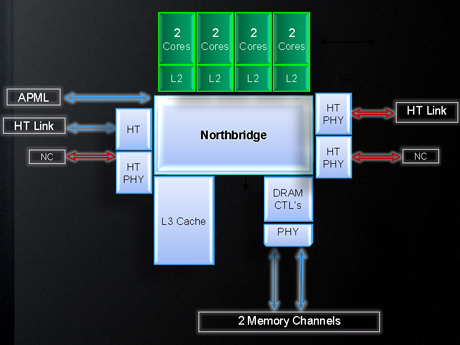

Valencia procesor je namijenjen postojećoj serverskoj C32 platformi, koja je 1-2 socket sistem (do 32 jezgre u sistemu). Procesori će biti podržani na trenutnim pločama putem nadogradnje BIOS-a, a podržavaju dvokanalnu UDIMM, RDIMM ili LRDIMM DDR3 memoriju maksimalne brzine 1600MHz. Maksimalno su podržana tri HyperTransport linka (do 6.4GT/s), dok će većina dizajna koristiti samo dva linka kako bi se ostalo unutr TDP-a. Tu je i Advanced Platform Management Link (APML) podrška, a podržani čipseti su SR5690 (42 PCI Express stazice), SR5670 (30 PCI Express stazica), SR5650 (22 PCI Express stazice) i SP5100 (southbridge).

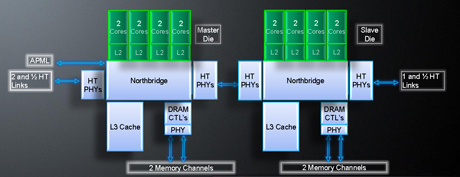

Interlagos procesori su namijenjeni G34 platformi, tj. 1-4 socket sistemima (do 64 jezgre u sistemu). Procesori su kompatibilni s G34 pločama putem BIOS nadogranje. Podržavaju četiri kanalnu UDIMM, RDIMM ili LRDIMM DDR3 memoriju maksimalne brzine 1600MHz. Četiri su eksterna HyperTransport linka ( 6.4 GT/s), plus interni die-to-die linkovi, a tu je i Advanced Platform Management Link (APML) podrška. Podržana kombinacija čipseta je SR56x0 + SP5100.

Za sada toliko o Bulldozeru, a nakon službenog predstavljanja idući tjedan će te moći detaljnije čitati i o konkretnim modelima, na kojim brzinama rade, cijenama i nadamo se vidjeti preformanse istih (ukoliko nam naš primjerak na vrijeme pristigne u lab).